JEDEC formally adopted its first SDRAM standard in 1993 and subsequently adopted other SDRAM standards, including those for DDR, DDR2 and DDR3 SDRAM.ĭouble data rate SDRAM, known as DDR SDRAM, was first demonstrated by Samsung in 1997. Today, virtually all SDRAM is manufactured in compliance with standards established by JEDEC, an electronics industry association that adopts open standards to facilitate interoperability of electronic components. The benefits of SDRAM's internal buffering come from its ability to interleave operations to multiple banks of memory, thereby increasing effective bandwidth.

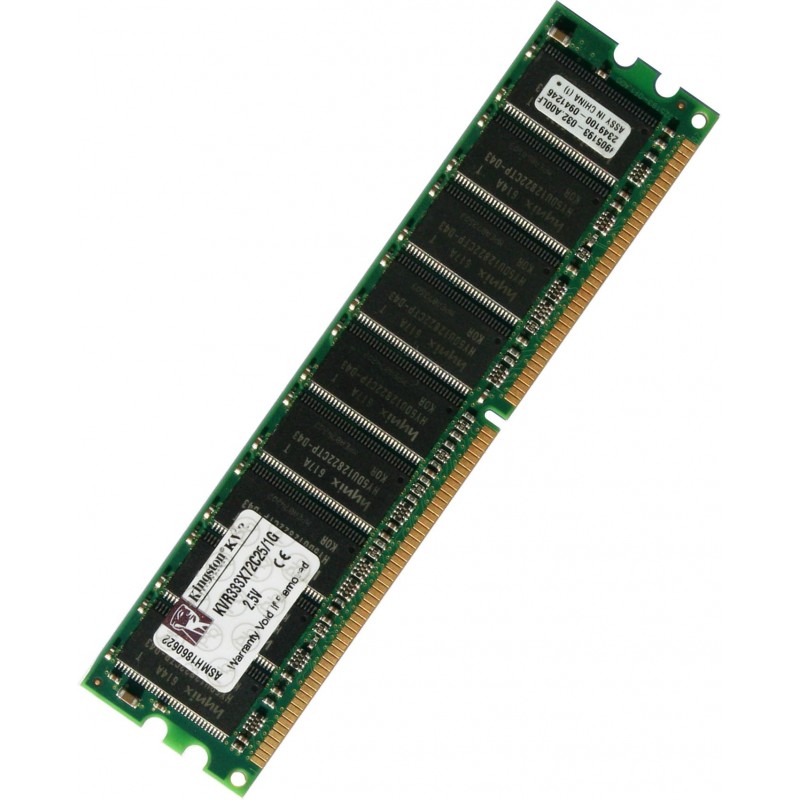

Indeed, early SDRAM was somewhat slower than contemporaneous burst EDO DRAM due to the additional logic. SDRAM latency is not inherently lower (faster access times) than asynchronous DRAM. By 2000, SDRAM had replaced virtually all other types of DRAM in modern computers, because of its greater performance. It was manufactured by Samsung Electronics using a CMOS (complementary metal–oxide–semiconductor) fabrication process in 1992, and mass-produced in 1993. The first commercial SDRAM was the Samsung KM48SL2000 memory chip, which had a capacity of 16 Mbit. In the mid-1970s, DRAMs moved to the asynchronous design, but in the 1990s returned to synchronous operation. The earliest DRAMs were often synchronized with the CPU clock (clocked) and were used with early microprocessors. For a pipelined read, the requested data appears a fixed number of clock cycles (latency) after the read command, during which additional commands can be sent.Įight Hyundai SDRAM ICs on a PC100 DIMM package For a pipelined write, the write command can be immediately followed by another command without waiting for the data to be written into the memory array. Pipelining means that the chip can accept a new command before it has finished processing the previous one. This allows SDRAMs to achieve greater concurrency and higher data transfer rates than asynchronous DRAMs could. The memory is divided into several equally sized but independent sections called banks, allowing the device to operate on a memory access command in each bank simultaneously and speed up access in an interleaved fashion. These commands can be pipelined to improve performance, with previously started operations completing while new commands are received. In SDRAM families standardized by JEDEC, the clock signal controls the stepping of an internal finite-state machine that responds to incoming commands. SDRAM has a synchronous interface, whereby changes on control inputs are recognised after a rising edge of its clock input. Here "off-heap buffers" is referring to direct memory, which is distinct from the filesystem cache.Synchronous dynamic random-access memory ( synchronous dynamic RAM or SDRAM) is any DRAM where the operation of its external pin interface is coordinated by an externally supplied clock signal.ĭRAM integrated circuits (ICs) produced from the early 1970s to early 1990s used an asynchronous interface, in which input control signals have a direct effect on internal functions only delayed by the trip across its semiconductor pathways. For instance, Elasticsearch uses off-heap buffers for efficient network communication, relies on the operating system’s filesystem cache for efficient access to files, and the JVM itself requires some memory too. The docs on this were adjusted to clarify this recently:Įlasticsearch requires memory for purposes other than the JVM heap and it is important to leave space for this. Thus you need at least twice as much RAM as your heap size (plus overhead in older versions) just for the process, and anything left over is available for the filesystem cache. In older versions the direct memory size is limited to be no larger than the heap and in newer versions it has a slightly more conservative limit. Heap size is fixed at startup but direct memory grows and shrinks as needed. Non-data nodes do not really need any filesystem cache as you say, but they still need direct memory for networking. Filesystem cache is not attributed to the process since it can all be discarded if needed (with a performance penalty obviously). Heap and direct memory are attributed to the Elasticsearch process if they add up to more than the available RAM then the process is liable to be killed. At a high level there are three main components to Elasticsearch's memory usage: the heap, direct memory, and filesystem cache (also known as page cache).

This is correct, but does not change the fact that the heap size must be limited to no more than 50% of the available RAM. Dedicated node types not holding data do not need to set aside 50% of RAM for the operating system page cache

0 kommentar(er)

0 kommentar(er)